Microchip Technology has expanded its PolarFire FPGA smart embedded video ecosystem to support developers requiring high-bandwidth video connectivity with low power consumption. The updated suite integrates hardware evaluation kits, development tools, IP cores, and reference designs aimed at accelerating the deployment of secure video pipelines.

The expansion introduces Serial Digital Interface (SDI) Receive (Rx) and Transmit (Tx) IP cores alongside a quad CoaXPress (CXP) board. These components are designed to support video pipelines for diverse applications, including medical diagnostics, low-latency imaging, and real-time camera connectivity for intelligent systems. The SDI IP cores provide Society of Motion Picture and Television Engineers (SMPTE) compliant transport for 1.5G, 3G, 6G, and 12G-SDI video.

According to the company, it currently offers the only FPGA-based quad CoaXPress solution capable of direct SLVS-EC and CoaXPress 2.0 bridging without requiring third-party IP. The ecosystem also features HDMI-to-SDI and SDI-to-HDMI bridging capabilities, supporting 4K and 8K video formats to facilitate high-resolution transport across professional and embedded platforms.

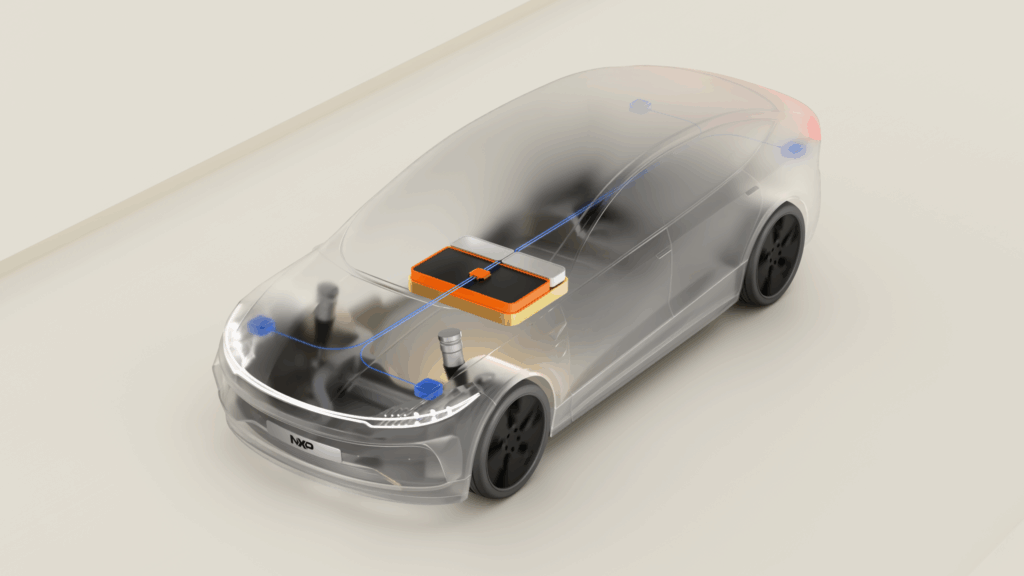

By utilizing the non-volatile architecture of PolarFire FPGAs, these solution stacks allow manufacturers to develop compact, fanless systems. The architecture incorporates layered security features and anti-tamper protection to safeguard hardware and data.

“Next-generation medical, industrial and robotic vision systems demand not only exceptional video quality but also uncompromising energy efficiency,” said Shakeel Peera, vice president of marketing for Microchip’s FPGA business unit. “The expansion of our PolarFire FPGA embedded video ecosystem underscores our commitment to delivering low-power solutions that are designed to enable customers to develop reliable and high-performance systems with robust connectivity and minimized energy consumption.”

The solution provides native support for Sony SLVS-EC sensors, offering a migration path for designs facing component discontinuations. To manage design complexity, developers can utilize the Libero Design Suite and SmartHLS high-level synthesis tool.